Series: Electronics and Energetics Vol. 27, No 4, December 2014, pp. 479 - 508

DOI: 10.2298/FUEE1404479T

# MODELING OF HOT-CARRIER DEGRADATION BASED ON THOROUGH CARRIER TRANSPORT TREATMENT

Stanislav Tyaginov<sup>1,2</sup>, Yannick Wimmer<sup>1</sup>, and Tibor Grasser<sup>1</sup>

<sup>1</sup>Institute for Microelectronics, TU Wien,

Gusshausstrasse 27-29, A-1040 Vienna, Austria

<sup>2</sup>A.F. Ioffe Physical-Technical Institute,

Polytechnicheskaya 26, St. Petersburg 194021, Russia

Abstract: We present and validate a physics-based model for hot-carrier degradation. The model is based on a thorough carrier transport treatment by means of an exact solution of the Boltzmann transport equation. Such important ingredients relevant for hot-carrier degradation as the competing mechanisms of bond dissociation, electron-electron scattering, the activation energy reduction due to the interaction of the dipole moment of the bond with the electric field as well as statistical fluctuations of this energy are incorporated in our approach. The model is validated in order to represent the linear drain current change in three different devices subjected to hot-carrier stress under different conditions. The main demand is that the model has to use a unique set of parameters. We analyze the importance of all the model ingredients, especially the role of electron-electron scattering. We check the idea that the channel/gate length of the device alone is not enough to judge whether electron-electron scattering is important or not and instead a combination of the device topology and stress conditions needs to be used.

**Keywords:** Hot-carrier degradation, interface traps, modeling, deterministic Boltzmann transport equation solver, MOSFET

Received October 6, 2014

Corresponding author: Stanislav Tyaginov

Institute for Microelectronics, TU Wien, Gusshausstrasse 27-29, A-1040 Vienna, Austria.

(e-mail: tyaginov@iue.tuwien.ac.at)

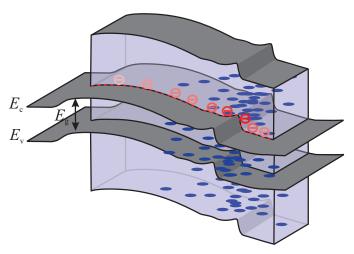

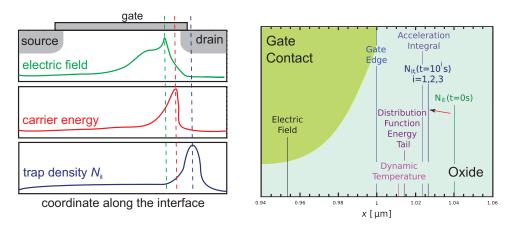

Fig. 1. A schematic representation of the MOSFET subjected to hot-carrier stress. The average carrier energy changes with the coordinate along the Si/SiO<sub>2</sub> interface, i.e. the carriers become hotter closer to the transistor drain. As a result, the bond-breakage rate and the interface state density are highest in this device area. The interface traps can capture charge carriers and become charged. They perturb the electrostatics of the device and scatter carriers, thereby degrading the device performance.

### 1 Introduction

Hot-carrier degradation (HCD) is a detrimental effect which degrades the metal-oxide-semiconductor field-effect transistor (MOSFET) performance and perturbs its characteristics. The damage is via generation of traps at or near the dielectric/Si interface of the MOSFET, see Fig. 1. These generated interface traps can capture electrons or holes and thus become charged. Therefore, the effect of charged defects on the device performance is twofold: they distort the local band-bending of the MOSFET and degrade the carrier mobility due to the additional scattering events at charges incorporated into the device. The former contribution results in the threshold voltage shift while the common action of both can be visible in degradation of the drain current, transconductance, on-state resistance, etc.

The HCD phenomenon was first reported in the 1970s [1–3] when transistor operating voltages were high. As a consequence, the high energetical fraction of the carrier ensemble was sufficiently populated. In other words, these hot carriers were able to efficiently trigger the bond dissociation events in a single collision with a Si-H bond, and thus this degradation mode was called "hot-carrier degradation". However, the aggressive scaling of MOSFETs has resulted, among other things, in substantially reduced operating/stress volt-

ages. Under these conditions, the hot carriers have negligible concentrations and the single-particle bond-breakage process thus has a rather low rate. Instead, several *colder carriers* can induce a multiple vibrational excitation (MVE) of the bond which triggers a bond rupture event [4–10]. Therefore, one can say that there are two competing HCD modes: single- and multiple-particle processes (SP- and MP-processes) which are triggered by hot and cold carriers.

As for the driving force of hot-carrier degradation, its understanding has also been changed. One of the pioneering HCD concepts [3, 11] – the so-called lucky electron model – states that an electron which has gained sufficiently high energy without loosing energy and scattering back into the channel can overcome the potential barrier at the Si/SiO<sub>2</sub> interface, penetrate the SiO<sub>2</sub> conduction band, and generate defect(s). Since this lucky electron obtains energy from the electric field, HCD was suggested to be field-driven. This understanding, however, needed to be reconsidered after a series of experiments published by the IBM group [12, 13]. The authors performed different types of stress (channel and substrate hot electron/hole stresses as well as Fowler-Nordheim and direct tunneling injections) and showed that in all cases the interface state generation rate depends only on the energy deposited by carriers and is insensitive to the electric field. This idea was implemented within the so-called energy driven paradigm proposed by Rauch and La Rosa [8, 14, 15].

The information on what exact portion of energy is deposited by carriers can only be obtained from a thorough carrier transport treatment. This task, however, is computationally very demanding—and this is the reason why a lot of hot-carrier degradation models are empirical or at best phenomenological [3, 16–22]. Furthermore, some simplifications are often made also in physics-based models of hot-carrier degradation. For instance, the SP- ans MP-mechanisms are competing pathways of the same bond dissociation reaction and need to be considered self-consistently. However, for the sake of simplicity in some HCD models these processes are treated as being independent [23–27]. The rates of these processes are affected by the scattering mechanisms with corresponding rates determined by the MOSFET configuration and applied voltages. In scaled devices electron-electron scattering (EES) plays a significant role and impacts the kinetics of defect generation [28, 29]. However, in early versions of one of the most successful HCD models developed by the Bravaix group, three HCD modes, namely driven by the SP-process, by EES, and by the MP-mechanisms are distinguished and considered independently [23, 24, 30].

Another controversial issue is the role of electron-electron scattering in the context of HCD. On the one hand, Rauch and La Rosa have shown that EES is responsible for a severe hot-carrier damage enhancement in devices with channel lengths shorter than 80-100 nm [8, 28, 29]. This scattering mechanism also defines the temperature behavior in ultra-scaled devices [8]. On the other hand, the Bravaix group has recently suggested that in their transistors the role of EES is dramatically overestimated. Instead, in short-channel MOSFETs HCD has been suggested to be driven by the two particle mixed mode process [31].

In this work we present a physics-based HCD model which relies on a thorough carrier transport treatment. This treatment is based on an exact solution of the Boltzmann transport equation. The model captures such ingredients relevant for hot-carrier degradation as competing mechanisms of Si-H bond-dissociation, electron-electron scattering, the bond-breakage activation energy reduction due to the interaction of the electric field with the dipole moment of the bond and statistical variations of this energy. To validate the model we use HCD data obtained in nanoscale transistors. We also analyze the role of each particular model component.

# 2 Characteristic features of hot-carrier degradation

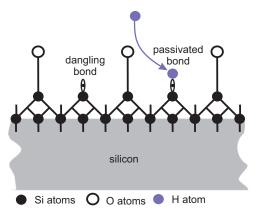

A principal question which needs to be addressed first of all is: "what is the criterion which allows us to separate hot and cold carriers?". Under "hot carriers" we understand those carriers with energies above the activation energy for the Si-H bond dissociation reaction, i.e. particles with energies above  $\sim 1.5 \, \mathrm{eV}$  [6, 32]. In fact, the interface between a crystalline Si substrate and an amorphous  $\mathrm{SiO}_2$  layed is imperfect. The disorder at the interface leads to Si- dangling bonds, see Fig. 2. These bonds can capture charge carriers. This process converts them to electrically active defects. To prevent this, hydrogen is intentionally incorporated into devices at the post-oxidation step. When H atoms terminate the Si- bonds, neutral and electrically passive Si-H bonds are formed, Fig. 2. The reverse process of bond depassivation can be triggered if a bond-breakage portion of energy is transferred to these Si-H bonds by e.g. hot carriers. The activation energy  $E_a$  for this process was shown to be  $\sim 1.5 \, \mathrm{eV}$  [6, 32].

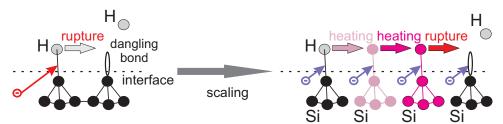

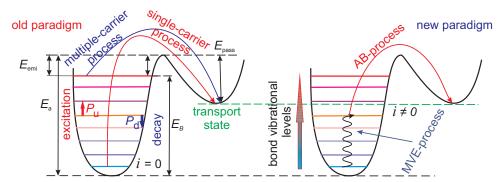

A solitary high energetical carrier can induce a bond-breakage event in a single collisions, i.e. can trigger the SP-process, see Fig. 3. Due to the huge disparity between the electron mass and the mass of the hydrogen nucleus and the total momentum conservation only a negligibly small portion of en-

Fig. 2. A dangling Si- bond is electrically active. i.e. can capture electrons/holes, become charged distort the MOSFET characteristics. To prevent this, hydrogen is intentionally introduced into the device. H atoms terminate dangling bonds and form electrically passive Si-H bonds.

Fig. 3. Bond dissociation by a solitary high energetical carrier and by a series of colder carriers. The former scenario is typical in long-channel MOSFETs subjected to hot-carrier stress at high voltages, while the latter one corresponds to short-channel devices stressed at low voltages.

ergy will be transferred to H, which is not sufficient for hydrogen release. Instead, most likely, the hot electron impinging on the bond can excite one of the bonding electrons to an antibonding (AB) state [33, 34]. Therefore, we further label this process as AB-mechanism. Since the activation energy for bond-breakage is  $\sim 1.5 \, \text{eV}$  hot-carrier degradation was expected to be almost completely suppressed if the applied source-drain  $V_{\rm ds}$  voltage is below 1.5 V. In practice, however, these expectations were debunked and HCD was shown to be quite severe even at low  $V_{\rm ds}$  [35]. There are two reasons responsible for substantial HCD in scaled devices: the multiple-carrier mechanism for bond dissociation and energy exchange mechanisms which populate the high energy fraction of the carrier ensemble. The multiple-carrier mechanism is related to the bombardment of the bond by a series of colder carriers which induce the multiple vibrational excitation (MVE) of the bond followed by

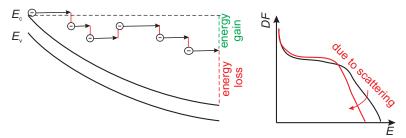

Fig. 4. A schematic representation of scattering mechanisms leading to energy loss. These mechanism depopulate the high energetical fraction of the carrier ensemble. In other words, they suppress the high-energy tails of the carrier energy distribution function.

hydrogen release, and hence by bond dissociation [6]. The MVE theory was first applied to interpret experimental data on hydrogen/deuterium desorption from H/D-passivated Si surfaces induced by electrons tunneling from a scanning tunneling microscope tip [36–38]. This theory was then adopted by the group of Hess for the case of Si/SiO<sub>2</sub> interfaces subjected to hot-carrier stress under conditions with low average carrier energies [33, 39, 40].

At the device level, the interaction between these single- and multiplecarrier pathways of bond dissociation leads to the change of the worst-case conditions (WCC) of HCD. Thus, in long-channel devices HCD is most severe when the average carrier energy has a maximum. In the case of n-MOSFETs the criterion chosen to judge on HCD severity is the substrate current [41–43]. This current consists of majority carriers generated by impact ionization. Both SP-process and impact ionization are characterized by rates of a same functional structure [29], and therefore the impact ionization induced substrate current is used to judge about the SP-process (i.e. HCD) intensity. As for p-MOSFETs, due to similar reasons the gate current is used as an indicator of the HCD severity [43-45]. In the former case the worst-case conditions are obtained when  $V_{\rm gs} \sim (0.4\text{-}0.5)V_{\rm ds}$  ( $V_{\rm gs}$  is the gate voltage) while for the latter case such an empirical interrelation between the voltages is not established. As for the case of scaled transistors, rather than the average particle energy the carrier flux is important. This is the case when  $V_{\rm gs} = V_{\rm ds}$  for both n- and p-MOSFETs [46–49].

As for the scattering mechanisms, they can populate the fraction of the carrier packet up to energies which are much higher than those available from the contact bias. Most important among them are impact ionization [50], Auger recombination [51], electron-phonon [52], and electron-electron scattering [53, 54]. Among these mechanisms electron-electron scattering is of special importance in ultra-scaled devices. EES also changes the temper-

ature behavior of HCD. In fact, in long-channel devices HCD becomes less pronounced at elevated temperatures [22, 41, 55–58]. The reason is that the scattering mechanisms depopulate the high energetical fraction of the carrier ensemble. Mathematically this means that high-energy tails of the carrier energy distribution function (DF) (which represents the probability to find carriers in the elementary energy range of [E; E + dE]) are suppressed due to these mechanisms, see Fig. 4. The rates of these processes increase with temperature, thereby making suppression of hot carriers more efficient at higher temperatures and, as a result, weaken hot-carrier degradation. In ultra-scaled devices, however, such events as electron-phonon scattering and scattering at ionized impurities are not efficient because a channel electron "meets" just a few dopant/lattice atoms. Vice versa, the carrier concentrations are high in these devices and the EES process can be quite efficient. EES was shown to populate the high-energy tails and therefore enforce hotcarrier degradation. Since the electron-electron interaction rate increases with temperature, EES leads to more severe HCD in scaled transistors. This trend is confirmed by the experimental data [59–61].

Since hot-carrier degradation is an energy driven process, carriers need to travel some distance to gain sufficient energy from the electric field. Such a behavior is typical also for the case of cold carriers because the rate of the MP-process depends on the carrier flux, i.e. also on the carrier velocity/energy. This determines one of the main features of hot-carrier degradation: the strong localization of the damage [62–64]. Let us consider an n-channel MOSFET with the electron packet moving from the source to the drain. It is well known that the maximum electric field, carrier temperature and the average carrier energy peak near the drain end of the gate. As a result, in the lucky electron model as well as in the energy driven paradigm the bond-breakage rate, and hence the interface state density  $N_{\rm it}$ , have their maxima also in this region, see Fig. 5. From Fig. 5, right one can also see that the maximum of the interface state density coincides neither with the electric field peak nor with the maximum of the carrier temperature/energy. Instead, we have recently shown [27, 65, 66] that the quantity which controls hot-carrier degradation is the carrier acceleration integral (AI) which will be introduced below.

All the peculiarities of hot-carrier degradation suggest that the bond-breakage kinetics are determined by the distribution of the carriers over the energy, that is, by the DF. Therefore, a proper description and modeling of HCD need to be based on a thorough carrier transport treatment.

Fig. 5. Left: Schematic representation of electric field, average carrier energy and interface state density profiles. Right: Positions of maxima of quantities crucial for HCD: electric field, carrier dynamic temperature, carrier average energy, interface trap density, etc. These exemplary simulations were preformed for a 5V n-MOSFET fabricated on a standard  $0.35\,\mu\mathrm{m}$  process with a gate length of  $0.5\,\mu\mathrm{m}$  subjected to hot-carrier stress at  $V_{\mathrm{ds}}=6.25\,\mathrm{V}$  and  $V_{\mathrm{gs}}=2.0\,\mathrm{V}$ .

# 3 The model

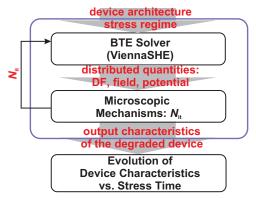

Our physics-based HCD model aims at covering and linking all the levels related to the hot-carrier degradation phenomenon starting at the microscopic level of defect generation which is connected via the carrier transport treatment with the modeling of the degraded devices. Thus, the model includes three corresponding modules, see Fig. 6. The transport kernel is realized on the platform of the deterministic Boltzmann transport equation solver ViennaSHE [67–69]. ViennaSHE incorporates full-band effects as well as such energy exchange mechanisms as scattering at ionized impurities, surface scattering, electron-electron and electron-phonon interactions as well as impact ionization. ViennaSHE is used to evaluate the carrier energy distribution functions for a particular device topology and given stress/operating conditions.

The obtained carrier DFs are then used to calculate the carrier acceleration integral which determines the rates of both AB- and MVE-mechanisms. This acceleration integral for electrons/holes and AB/MVE-processes is defined as:

$$I_{\text{ab/mve}}^{\text{(e/h)}} = \int_{E_{\text{th}}}^{\infty} f^{\text{(e/h)}}(E)g^{\text{(e/h)}}(E)\sigma_{\text{ab/mve}}^{\text{(e/h)}}(E)v(E)dE, \tag{1}$$

Fig. 6. Our physics-based HCD model contains three main modules: a description of the defect generation kinetics, the carrier transport kernel, and modeling of the degraded devices. The model is implemented into the deterministic solver of the Boltzmann transport equation ViennaSHE.

where  $f^{(e/h)}(E)$  stands for the DFs,  $g^{(e/h)}(E)$  the corresponding density-of-states,  $\sigma_{\rm ab/mve}(E)$  the reaction cross section, while v(E) the group velocity. To model the reaction cross section in the case of the AB-process we use a Keldysh-like expression [4, 50]:

$$\sigma_{\rm ab/mve}^{\rm (e/h)}(E) = \sigma_{\rm 0,ab/mve}^{\rm (e/h)}(E - E_{\rm th,ab/mve})^{p_{\rm it}}.$$

(2)

Here  $\sigma_{0,ab/mve}$  is a prefactor,  $E_{th,ab/mve}$  is the bond-breakage energy, while  $p_{\rm it} = 11$ . Note that the activation energy can vary statistically because of the structural disorder at the Si/SiO<sub>2</sub> interface and due to the interaction of the electric field with the dipole moment of the bond. As for the MVEmechanism we consider the Si-H bond as a truncated harmonic oscillator characterized by a system of eigenstates in the corresponding potential profile well, see Fig. 7. Thus, in the case of the MVE-process the threshold energy is the distance between the oscillator levels  $\hbar\omega$ . It is important to emphasize that in the previous version of our HCD model we considered the singleand multiple-carrier mechanism as independent processes and the cumulative interface state density  $N_{\rm it}$  was calculated as the sum of SP- and MP-induced contributions weighted with some probability factors (fitting parameters of the model), cf. [26, 27], Fig. 7, left. In the current version of our model we incorporate all the superpositions of the AB- and MVE-mechanisms [70, 71], see Fig. 7, right. In other words, first the bond can be heated by several colder particles (which trigger the MVE-mechanism) to an intermediate level with the index i and then dissociated by a single carrier with relatively high energy. If the bond is in the ith eigenstate the potential barrier for the

Fig. 7. The Si-H bond as truncated harmonic oscillator. **Left**: In the previous version of our HCD model the single- and multiple-carrier processes are modeled as independent processes. **Right**: In the most recent version of our model these processes are considered as competing pathways of the same bond-breakage reaction. We take into account all the possible superpositions of the AB- and MVE-mechanisms when first the bond is pre-heated by a series of low energetical carriers (the MVE-mode) and then ruptured by a solitary hot carrier (AB-mechanism).

proton which separates this state and the transport mode is reduced, and thus the acceleration integral is:

$$I_{ab,i} = \int f(E)g(E)\sigma_0(E - E_a + E_i + d \times E_{ox})^{p_{it}}v(E)dE.$$

(3)

Here  $E_i$  is the level position and the term  $d \times E_{ox}$  represents the activation energy reduction caused by the interaction of the dipole moment of the bond d with the oxide electric field  $E_{ox}$ . As a result, bond dissociation from the intermediate level i requires a lower carrier energy and the probability that the ensemble contains particles with energies above this threshold is higher. The bond-breakage rate from each particular level is modeled as

$$R_{\text{ab},i} = w_{\text{th}} \exp\left[-\left(E_{\text{a}} - E_{i} - d \times E_{\text{ox}}\right)/k_{\text{B}}T\right] + I_{\text{AB},i}.$$

(4)

where the first term (with the attempt frequency  $w_{\rm th}$ ) corresponds to the thermal activation of the H atom over the potential barrier, while the acceleration integral  $I_{{\rm AB},i}$  represents the effect of hot carriers.

The bond dissociation kinetics are described by the set of rate equations:

$$\frac{dn_0}{dt} = P_d n_1 - P_u n_0 - R_{a,0} n_0 + R_{p,0} N_{it}^2$$

$$\frac{dn_i}{dt} = P_d (n_{i+1} - n_i) - P_u (n_i - n_{i-1}) - R_{a,i} n_i + R_{p,i} N_{it}^2$$

$$\frac{dn_N_l}{dt} = P_u n_{N_{l-1}} - P_d n_N_l - R_{a,N_l} n_{N_l} + R_{p,N_l} N_{it}^2.$$

(5)

Note that in contrast to the system used in the Bravaix model we also consider passivation reactions to each particular level i with the corresponding rates  $R_{\mathrm{p},i}$ . In (5)  $n_i$  are the level occupation numbers,  $N_l$  labels the last bonded state and  $P_{\mathrm{u}}$  and  $P_{\mathrm{d}}$  are the rates of the multivibrational mode excitation/deexcitation processes:

$$P_{\rm u} = \omega_{\rm e} \exp\left(-\hbar\omega/k_{\rm B}T_{\rm L}\right) + I_{\rm MVE},$$

$$P_{\rm d} = \omega_{\rm e} + I_{\rm MVE}$$

(6)

with  $\omega_{\rm e}$  being the reciprocal phonon life-time.

We solve the system (5) by taking into account the huge disparity between the characteristic times which describe the establishment of the oscillator steady-state and those which correspond to the bond rapture/passivation processes.

$$\frac{dN_{it}}{dt} = (N_0 - N_{it}) R_a - N_{it}^2 R_p,$$

(7)

where  $N_0$  is the concentration of passivated Si-H bonds and the cumulative bond-breakage rate is:

$$R_{\rm a} = \frac{1}{k} \sum_{i} R_{\rm a,i} \left( \frac{P_{\rm u}}{P_{\rm d}} \right)^{i}, \tag{8}$$

where k is a normalization prefactor:

$$k = \sum_{i} \left(\frac{P_{\rm u}}{P_{\rm d}}\right)^{i}.$$

(9)

As for the cumulative passivation rate  $R_p = \sum_i P_i$ , without loss of generality, one may represent the P rate by the Arrhenius term for thermal activation over a single barrier, i.e.

$$R_{\rm p} = \nu_{\rm p} \exp(-E_{\rm pass}/k_{\rm B}T_{\rm L}),\tag{10}$$

where  $\nu_{\rm p}$  is a prefactor which designates the attempt frequency.

The system (5) is finally solved analytically:

$$N_{\rm it}(t) = \frac{\sqrt{R_{\rm a}^2/4 + N_0 R_{\rm a} R_{\rm p}}}{R_{\rm p}} \frac{1 - f(t)}{1 + f(t)} - \frac{R_{\rm a}}{2R_{\rm p}},$$

$$f(t) = \frac{\sqrt{R_{\rm a}^2/4 + N_0 R_{\rm a} R_{\rm p}} - R_{\rm a}/2}{\sqrt{R_{\rm a}^2/4 + N_0 R_{\rm a} R_{\rm p}} + R_{\rm a}/2} \exp\left(-2t\sqrt{R_{\rm a}^2/4 + N_0 R_{\rm a} R_{\rm p}}\right).$$

(11)

It is important to emphasize that this solution transforms to the expression obtained within the previous version of our HCD model when the AB- and MVE-mechanisms were considered independently, i.e. if the rate of one of the processes is neglected, cf. [26, 27].

The activation energy reduction due to the interaction between the oxide electric field and the dipole moment of the Si-H bond is modeled as  $d \times E_{\rm ox}$ , cf. (3), see [72, 73]. The dipole moment of the bond is a fitting parameter of the model. In the case of the SiON gate films of n-MOSFETs employed to validate the model we use a value of d=0.044 which is slightly different from that used in the Bravaix model (0.056) [73]. As for the activation energy fluctuations we assume that  $E_{\rm a}$  obeys a Gaussian distribution with the mean values and standard deviation of  $\langle E_{\rm a} \rangle = 1.5\,{\rm eV}$  and  $\sigma_{\rm E} = 0.15\,{\rm eV}$ . These values are in good agreement with experimentally observed ones [74–76]. The effect of the activation energy dispersion was incorporated in the manner that the range  $[\langle E_{\rm a} \rangle - 3\sigma_{\rm E}; \langle E_{\rm a} \rangle + 3\sigma_{\rm E}]$  was discretized and for each discretization point we evaluated the interface trap density profile  $N_{\rm it}(x)$  according to (11) weighted with the Gaussian distribution.

#### 4 Results and Discussion

The model was validated in a manner to capture HCD in different devices stressed under various hot-carrier conditions but using a unique set of the model parameters. The aim was also to analyze the importance of each of the model ingredients, especially the role of the EES process in the context of hot-carrier degradation.

# 4.1 Experiment

To validate the model we used SiON n-MOSFETs of an identical architecture but with different gate lengths, i.e.  $L_{\rm G}=65,\,100,\,$  and 150 nm, which corresponds to the channel lengths of  $\sim 45,\,80,\,$  and 120 nm. A 2.5 nm thick SiON gate film was fabricated by a decoupled plasma nitridation process followed by post-nitridation annealing. The devices were subjected to hot-carrier stress at the worst-case HCD conditions corresponding to these particular MOSFETs and at two different drain voltages:  $V_{\rm ds}=1.8$  and 2.2 V for approximately 8 ks at room temperature. During stress the normalized linear drain current change, i.e.  $|I_{\rm dlin}(t)-I_{\rm dlin,0}|/I_{\rm dlin,0}$ , was recorded as a function of stress time (here  $I_{\rm dlin}(t)$  is the linear drain current at stress time t, while  $I_{\rm dlin,0}$  is the drain current measured in the fresh device).

The MOSFET with  $L_{\rm G}=65\,{\rm nm}$  was treated as a short-channel device with corresponding worst-case scenario realized when  $V_{\rm gs}=V_{\rm ds}$ . As for the 150 nm counterpart it was not obvious whether this MOSFET belongs to the long-channel devices or not. To check this, the substrate current was recorded as a function of  $V_{\rm ds}$  and  $V_{\rm gs}$ . The substrate current maximum was observed at  $V_{\rm gs}\sim V_{\rm ds}/2$ . This finding suggests that this is a long-channel MOSFET with the corresponding worst-case combination of stress voltages. In the case of the 100 nm transistor the substrate current was at maximum when  $V_{\rm gs}=2/3V_{\rm ds}$  and this relation between  $V_{\rm ds}$  and  $V_{\rm gs}$  was used to stress this transistor.

#### 4.2 The distribution functions

The device architecture was obtained using the Sentaurus Process simulator [77]. Since the carrier distribution functions are very sensitive to doping profiles, the process and device simulators (i.e. Sentaurus Process and ViennaSHE) were coupled and calibrated in a fashion to represent the current-voltage characteristics of the fresh device.

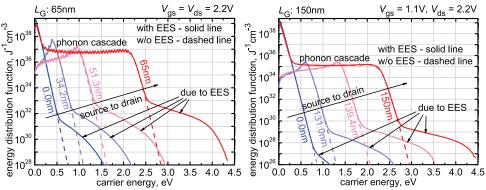

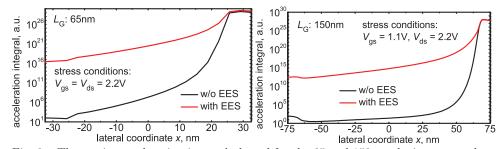

A series of electron DFs computed with ViennaSHE for 65 and 150 nm MOSFETs stressed at  $V_{\rm ds} = 2.2\,\rm V$  are shown in Fig. 8. These DFs are calculated with and without EES and plotted in different positions in the device (in the graph the distance from the source to the position where the DF is evaluated is marked). The DFs are severely non-equilibrium, i.e. they show a plateau at moderate energies and prominent high-energy tails. These high-energy tails become more populated due to electron-electron scattering, and thus one concludes that the effect of EES substantially changes the shape of the distribution functions. These changes are especially strong near the drain but less pronounced near the source. One can also see that the onset of the characteristic hump visible in the high-energy tails (which is a result of EES) occurs at higher energies in the 150 nm device, and this suggests that the effect of EES is expected to be weaker in longer transistors. Note that all the DFs still have a Maxwellian rudiment at low energies. This rudiment becomes longer near the source, i.e. the distribution functions are closer to the equilibrium ones.

These distribution functions are used to evaluate the carrier acceleration integrals. The AIs evaluated for the ground state and for the case of the same devices and same stress conditions as Fig. 8 are plotted in Fig. 9. To check the effect of EES the AIs obtained without this scattering mechanism are also shown. One can see that EES substantially changes the AI shape. The

Fig. 8. A family of the carrier distribution functions calculated for the 65 and 150 nm MOSFETs stressed at the corresponding worst-case HCD conditions at  $V_{\rm ds}=2.2\,\rm V$  with and without electron-electron scattering. The DFs are plotted in different positions of the transistors at the SiON/Si interface.

impact of EES on the AI is weaker in longer devices. This finding correlates with the DFs shown in Fig. 8 where the high-energy tails are more populated by electron-electron scattering in the shorter MOSFET.

# 4.3 The $\Delta I_{\text{dlin}}$ data and $N_{\text{it}}(x)$ profiles

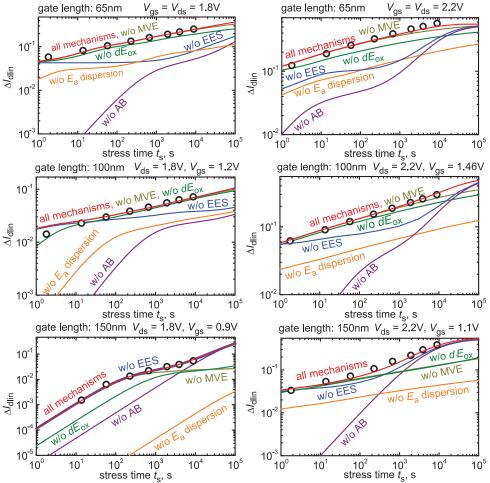

Fig. 10 summarizes the experimental linear drain current change plotted vs. stress time for all the devices and all combinations of stress voltages as well as simulated  $\Delta I_{\rm dlin}(t)$  curves. One can see that agreement between experiment and theory is rather good. It is also important to emphasize that the model uses a unique set of parameters for all devices/conditions. To

Fig. 9. The carrier acceleration integral plotted for the 65 and 150 nm devices stressed at  $V_{\rm ds}=2.2\,{\rm V}$  vs. the lateral coordinate x along the dielectric/Si interface. These integrals are evaluated with and without electron-electron scattering. One can see that the effect of EES is strong. The source corresponds to x=-32.5 and -75 nm for 65 and 150 nm devices, respectively.

Fig. 10. The normalized change of the linear drain  $(|I_{\rm dlin}(t) - I_{\rm dlin,0}|/I_{\rm dlin,0})$  current as a function of stress time: the experimental data vs. the simulated curves plotted for three n-MOSFETs with gate lengths of 65, 100, and 150 nm stressed at their HCD worst-case conditions and two different  $V_{\rm ds}=1.8$  and 2.2 V. One can see that agreement between experiment and simulations is good. To analyze the importance of particular model components we have also plotted  $\Delta I_{\rm dlin}(t)$  curves obtained neglecting one of the model components such as AB- and MVE-mechanisms, EES, the  $d \times E_{\rm ox}$  activation energy reduction, and its dispersion.

analyze the importance of each particular model component (competing ABand MVE-processes, electron-electron scattering, interaction of the dielectric electric field with the dipole moment of the bond, and the activation energy dispersion) we have also simulated  $\Delta I_{\rm dlin}(t)$  dependences disregarding one of these components.

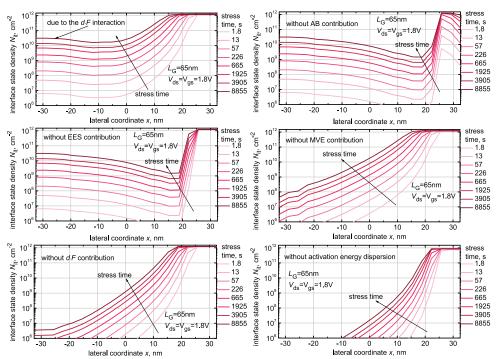

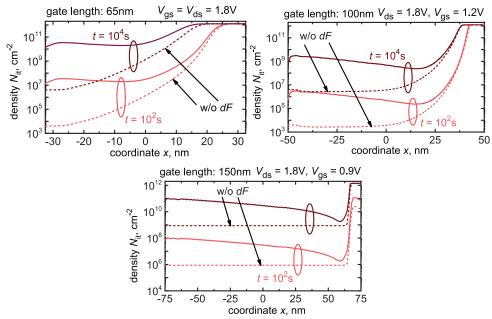

One can see that even in the case of scaled devices with  $L_{\rm G}=65\,{\rm nm}$ the AB-process plays a dominant role, especially at short stress times but is less pronounced at longer stress times. This tendency can be understood if we consider the  $N_{\rm it}(x)$  profiles. Fig. 11 depicts these profiles obtained for the 65 nm transistor stressed at  $V_{\rm gs} = V_{\rm ds} = 1.8\,{\rm V}$  for each stress time step with and without one of the model ingredients. One can see that the concentration  $N_{\rm it}$  peaks near the drain, while near the source  $N_{\rm it}$  is lower and the profile is almost flat. The drain peak corresponds to the effect of hot carriers. Indeed, near the drain carriers are characterized by most pronounced high-energy tails of the distribution functions, cf. Figs. 8, 9. Thus, if the AB-mechanism rate is suppressed the drain peak appears to be narrower and weaker. At the same time, the source acts as a reservoir of thermalized carriers with DFs revealing almost Maxwellian behavior. Note that already at a stress time of 1.8s the drain peak is saturated, i.e.  $N_{\rm it}$  does not change with either the lateral coordinate x nor with stress time. As a result, short-term HCD is determined by the propagation of the  $N_{\rm it}$  front towards the device center, and hence, ignoring of the AB-process leads to a sever  $\Delta I_{\text{dlin}}$  underestimation especially at short times.

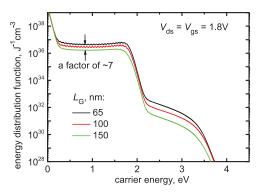

It is important to emphasize that the contribution of the AB-mechanism is more pronounced in shorter devices. At a first glance this trend contradicts the commonly used idea that hot-carrier degradation is controlled by the AB-process in long-channel devices and the role of this mechanism becomes less pronounced if device dimensions shrink. To analyze this behavior in more detail we also have plotted the electron DFs for all three devices and the same combination of stress voltages ( $V_{\rm ds} = V_{\rm ds} = 1.8\,\rm V$ ), see Fig. 12. One can see that the DFs have lower values in the case of longer devices. Thus, the distribution function values calculated for the 65 and 150 nm device can differ by a factor of  $\sim 7$  at moderate energies and this difference is even more pronounced at high-energy tails. As the AB-mechanism is very sensitive to the high-energy tails, its relative contribution is less important in the case of longer MOSFETs.

Ignoring electron-electron scattering leads to the same tendencies as suppressing the AB-process rate, see Fig. 10 and Fig. 11. For instance, one can see that the drain  $N_{\rm it}$  maximum also becomes narrower, while  $\Delta I_{\rm dlin}$  appears to be underestimated especially at moderate stress times (at longer times the EES effect is weaker). This is because EES populates the high energy fraction of the carrier ensemble (see Fig. 8), and therefore strengthens the AB-mechanism. It is important to emphasize that the contribution of electron-electron scattering is less pronounced in longer devices. For exam-

Fig. 11. The interface state density  $N_{\rm it}(x)$  profiles plotted for the 65 nm transistor subjected to hot-carrier stress at  $V_{\rm gs}=V_{\rm ds}=1.8\,{\rm V}$  for all stress time steps obtained with the "full" model and neglecting one of the model components. The source corresponds to  $x=-32.5\,{\rm nm}$ .

ple, the EES effect is weak in the 100 nm transistor at  $V_{\rm ds} = 1.8\,\rm V$  and  $V_{\rm gs} = 1.2\,\rm V$  and can be neglected in the 150 nm counterpart at both combinations of  $V_{\rm ds}$  and  $V_{\rm gs}$ . This tendency can be explained from an analysis of electron DFs plotted with and without EES, see Fig. 8. One can see that at the same stress voltages the onset of the EES-related hump visible in high-energy tails occurs at higher energies, thereby leading to a weaker EES impact.

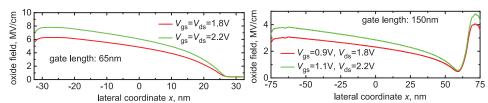

The interaction of the electric field with the dipole moment of the bond leads to a secondary maximum observed in the  $N_{\rm it}(x)$  profiles near the drain Fig. 11. This situation is typical for all three devices stressed under different interrelations between  $V_{\rm ds}$  and  $V_{\rm gs}$ , see Fig. 13. This maximum coincides with the the maximum of the electric field which is also located near the source. To illustrate this, we have evaluated the electric field as a function of the lateral coordinate x along the interface for two devices (with gate lengths of 65 and 150 nm) for both combinations of stress voltages. One can see that in all four cases the electric field profiles reveal maxima near the source and the positions of these maxima coincide with the  $N_{\rm it}$  peak positions, cf. Fig.

Fig. 12. The carrier energy distribution functions computed for  $V_{\rm gs} = V_{\rm ds} = 1.8\,\rm V$  for all the devices for the drain area. One can see that at the same combination of applied voltages DFs are characterized by lower values.

13. If the  $d \times E_{\rm ox}$  activation energy reduction is ignored, the interface states density profiles are flat in the source section of the device. These constant  $N_{\rm it}(x)$  dependences are related to the saturated MVE-process. Note that quite a similar behavior of  $N_{\rm it}$  curves was reported in our previous works also for the case of a long-channel n-MOSFET with the gate length of  $0.5\,\mu{\rm m}$  [25–27] as well as independently by the Bravaix group [78]. The secondary  $N_{\rm it}$  maximum is more pronounced at long stress times and thus determines the long-term linear drain current change, see Fig. 10 .

As for the MVE-process, Fig. 10 suggests that its role becomes more important in longer devices. At a first glance, this results appears to be quite unusual because the MVE-process is assumed to be dominant in shortchannel devices. The reason is the same as the explanation why the ABmechanism contribution is more pronounced in MOSFETs with longer  $L_{\rm G}$ . At a fixed pair of  $V_{\rm ds}$ ,  $V_{\rm gs}$  high-energy tails of the DFs are less populated in longer MOSFETs, cf. Fig. 12. As a consequence, the contribution of the ABprocess becomes less prominent while the relative role of the MVE-process increases. Due to the same reason, since the AB-mechanism is dominant at short stress times, the MVE-process contributes in HCD at longer stress times. Ignoring the effect of the MVE-mechanism leads to a discrepancy which is most pronounced between the transistor source and center. Near the drain carriers are hot enough and bond dissociation events are predominantly triggered by solitary carriers without pre-heating of the bonds by the MVEprocess. This is not the case in the rest of the device where excitation of bond vibrational modes becomes more important.

As for the activation energy dispersion, ignoring this ingredient leads

Fig. 13. The interface states density  $N_{\rm it}(x)$  profiles plotted for all devices stressed under  $V_{\rm ds}=1.8{\rm V}$  for 100 s and 10 ks considering and ignoring the effect of the activation energy reduction due to the interaction of the electric field with the dipole moment of the bond. In all cases the  $d\times E_{\rm ox}$  reduction leads to a secondary  $N_{\rm it}$  peak located near the source. The position of this peak coincides with the position of the electric field maximum. If the  $d\times E_{\rm ox}$  effect is not considered, the  $N_{\rm it}(x)$  profiles are flat in the source section (source is in the left) of the device and correspond to the saturated MVE-mechanism. The source position corresponds to x=-32.5,-50, and -75 nm for the 65, 100, and 150 nm n-MOSFETs, accordingly.

to substantial underestimation of  $\Delta I_{\text{dlin}}$  observed in the entire stress time slot, see Fig. 10. This is also confirmed by the  $N_{\text{it}}(x)$  profiles. One can see that the drain  $N_{\text{it}}$  maximum is almost not affected by the activation energy dispersion. This is because in the drain region of the device carriers are rather hot, the AB-process is saturated, and hence a further reduction of the activation energy does not substantially impact the bond-breakage kinetics in this transistor section.

## 4.4 The role of electron-electron scattering

The previous results show that the effect of electron-electron scattering can be strong or weak in the same device subjected to various combinations of voltages Fig. 10. Thus, in the case of the 150 nm MOSFET the contribution of electron-electron scattering can be neglected when the device is stressed

Fig. 14. The electric field profiles evaluated for the 65 and 150 nm n-MOSFETs for both combinations of stress voltages. One can see that in all cases the electric field peaks near the source which leads to a secondary maximum observed in  $N_{\rm it}$  profiles at the same position. The source position corresponds to x=-32.5 and 75 nm for the 65 and 150 nm n-MOSFETs, accordingly.

at  $V_{\rm gs}=0.9\,{\rm V}$  and  $V_{\rm ds}=1.8\,{\rm V}$ , while the EES contribution is stronger if the applied voltages are higher:  $V_{\rm gs}=1.1\,{\rm V}$  and  $V_{\rm ds}=2.2\,{\rm V}$ . This trend hints that rather than the gate/channel length alone a superposition of the device architecture and stress conditions is important.

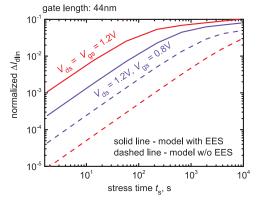

To check this idea we have virtually fabricated a series of n-MOSFETs (using the Sentaurus Process simulator) by the same process flow as 65, 100, and 150 nm transistors but with gate lengths covering a wider range. We used devices with  $L_{\rm G}=44$ , 200, and 300 nm. According to the work by Rauch *et al.* [28, 29], EES starts to play an important role when the channel length is below 70-100 nm, just within the range used in this work.

Fig. 15. The normalized linear drain current change simulated for the n-MOSFET with a gate length of 44 nm for two stress conditions: for  $V_{\rm gs}=0.8\,\rm V,\,V_{\rm ds}=1.2\,\rm V$  and for  $V_{\rm gs}=V_{\rm ds}=1.2\,\rm V$  with and without EES. One can see that in both cases EES plays an important role

Fig. 15 shows the relative change of the linear drain current plotted as a function of stress time for the 44 nm n-MOSFET simulated with and without electron-electron scattering for  $V_{\rm gs} = 0.8 \, {\rm V}, \, V_{\rm ds} = 1.2 \, {\rm V}$  and for  $V_{\rm gs} = V_{\rm ds} = 0.8 \, {\rm V}$

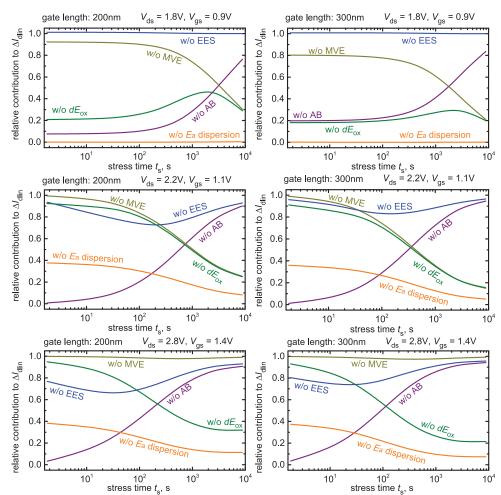

Fig. 16. The ratios between  $\Delta I_{\rm dlin}$  calculated neglecting one of the model components to that computed with the "full" model obtained for two transistors with  $L_{\rm G}=200$  and 300 nm for their worst-case conditions and three different drain voltages:  $V_{\rm ds}=1.8,\ 2.2,$  and  $2.8\ {\rm V}.$

1.2 V, One can see that even at low voltages as  $V_{\rm gs} = 0.8$  V,  $V_{\rm ds} = 1.2$  V the role of EES is prominent and this mechanism cannot be ignored.

Further, for the 200 and 300 nm devices we plot the relative contribution of the model ingredients, i.e. we analyze the ratios between  $\Delta I_{\rm dlin}$  computed neglecting one of the model components and that obtained with the "full" model. Fig. 16 depicts these ratios for the worst-case HCD conditions typical for these devices ( $V_{\rm gs} = V_{\rm ds}/2$ ) and three different values of the drain voltage:  $V_{\rm ds} = 1.8, 2.2$ , and 2.8 V. One can see that the EES effect can be

neglected at low drain voltages ( $V_{\rm ds}=1.8\,{\rm V}$ ) in both devices. At higher  $V_{\rm ds}$ , however, EES starts to play a significant role. For instance, neglecting EES in the 200 nm MOSFET stressed at  $V_{\rm ds}=2.2$  and 2.8 V leads to a severe  $\Delta I_{\rm dlin}$  underestimation of more than 20% and 30%, respectively in the time slot of 10-100 s. In the 300 nm counterpart the contribution of EES is less pronounced but still prominent. Thus, if  $V_{\rm ds}=2.8\,{\rm V}$ , a discrepancy between  $\Delta I_{\rm dlin}(t)$  curves simulated with and without EES will be more than 25%.

To summarize, the analysis of EES over a wide range of gate lengths (we used  $L_{\rm G}=44,\,65,\,100,\,150,\,200,$  and 300 nm) and different combinations of applied voltages suggests that only a consistent consideration of the device topology and stress conditions allows us to judge whether EES is important or not.

#### 5 Conclusions

We have presented and validated a new version of our physics-based model for hot-carrier degradation. Within our model three main levels relevant for HCD are covered and linked, namely the microscopic level of defect generation, carrier transport, and modeling of the degraded devices. The carrier transport kernel is realized using the deterministic Boltzmann transport equation solver ViennaSHE, which incorporates full-band effects and various scattering mechanisms, in particular the electron-electron interaction. The model consolidates such important ingredients relevant for hot-carrier degradation as the two competing mechanisms of Si-H bond dissociation, electron-electron scattering, the reduction of the bond-breakage activation energy due to the interaction of the dipole moment of the bond with the electric field, and statistical fluctuations of this energy.

Our model was validated against HCD experimental data obtained from three n-MOSFETs of an identical architecture but with different gate lengths of 65, 100, and 150 nm. The devices were stressed at their HCD worst-case conditions and two different drain voltages, namely at  $V_{\rm ds}=1.8$  and 2.2 V. In all cases the model was able to successfully represent the relative linear drain current shift using a unique set of parameters. In order to analyze the importance of each of the model ingredients,  $\Delta I_{\rm dlin}(t)$  curves obtained disregarding one of these ingredients were also evaluated.

We have shown that even in as short devices as n-MOSFETs with a gate length of 65 nm the bond-dissociation process triggered by a solitary hot carrier can play a dominant role when the transistor is stressed at a high voltage (e.g. at  $V_{\rm ds}=1.8\,\rm V$ ). Quite intriguingly, the multiple vibrational excitation

bond-breakage mechanism tends to be more important in longer transistors. At a first glance, this result contradicts the commonly used idea that in short-channel devices HCD is dominated by the MVE-process, while the AB-mechanism drives hot-carrier degradation in long-channel counterparts. Our findings can be understood in the context of the carrier distribution functions. If a combination of  $V_{\rm gs}, V_{\rm ds}$  is fixed and DFs calculated for MOS-FETs with different channel lengths are compared, one concludes that the high energetical fraction of the carrier ensemble is less populated in longer devices under the same voltages. As a result, the relative contribution of the AB-process decreases while the role of the MVE-mechanism increases. The same argument explains why the role of electron-electron scattering becomes less important in longer MOSFETs. As for the interaction of the electric field with the dipole moment of the bond, this effect leads to a secondary maximum observed in  $N_{\rm it}$  profiles near the source. This maximum becomes more pronounced with stress time and determines long-term HCD. Neglecting the activation energy dispersion leads to a severe  $\Delta I_{\rm dlin}$  underestimation within the entire stress time window.

To analyze the role of EES in more detail a series of transistors of the same architecture but with gate lengths of 44, 200, and 300 nm was used. It was shown that in the case of the 44 nm device the EES contribution is prominent even at such low voltages as  $V_{\rm gs}=0.8\,\rm V$  and  $V_{\rm ds}=1.2\,\rm V$ . As for the 200 nm MOSFET, EES can be neglected in the case of  $V_{\rm gs}=0.9\,\rm V$  and  $V_{\rm ds}=1.8\,\rm V$ . However, electron-electron scattering appears to be very important if  $V_{\rm gs}=1.4\,\rm V$  and  $V_{\rm ds}=2.8\,\rm V$ , i.e.  $\Delta I_{\rm dlin}$  calculated without EES is lower by more than 30% than that obtained with the effect of EES. In the 300 nm counterpart neglecting EES leads to a more than 20% underestimation of  $\Delta I_{\rm dlin}$  at  $V_{\rm gs}=1.4\,\rm V$  and  $V_{\rm ds}=2.8\,\rm V$ . These findings suggest that rather than the channel/gate length alone a combination of the device architecture and stress conditions is needed to judge on the importance of electron-electron scattering.

# Acknowledgment

The authors acknowledge support by the Austrian Science Fund (FWF), grants P23598 and P26382, and the European Community FP7 projects  $N^{\rm o}$  261868 (MORDRED) and 619246 (ATHENIS\_3D).

## References

- [1] E. Nicollian, C. Berglund, P. Schmidt, and J. Andrews, "Electrochemical Charging of Thermal SiO<sub>2</sub> Films by Injected Electron Currents," *Journ. Appl. Phys.*, vol. 42, no. 12, pp. 5654–5664, 1971.

- [2] T. Ning, P. Cook, R. Dennard, C. Osburn, S. Schuster, and H. Yu, "1  $\mu$ m MOST VLSI Technology Part IV: Hot-electron Design Constraints," *IEEE Trans. Eelectron Dev.*, vol. 26, pp. 346–353, 1979.

- [3] C. Hu, "Lucky Electron Model for Channel Hot Electron Emission," in *Proc. International Electron Devices Meeting (IEDM)*, pp. 22–25, 1979.

- [4] W. McMahon, K. Matsuda, J. Lee, K. Hess, and J. Lyding, "The Effects of a Multiple Carrier Model of Interface States Generation of Lifetime Extraction for MOSFETs," in *Proc. Int. Conf. Mod. Sim. Micro*, vol. 1, pp. 576–579, 2002.

- [5] W. McMahon and K. Hess, "A Multi-Carrier Model for Interface Trap Generation," *Journal of Computational Electronics*, vol. 1, no. 3, pp. 395–398, 2002

- [6] A. Bravaix, C. Guerin, V. Huard, D. Roy, J. Roux, and E. Vincent, "Hot-carrier Acceleration Factors for Low Power Management in DC-AC Stressed 40nm NMOS Node at High Temperature," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 531–546, 2009.

- [7] A. Bravaix and V. Huard, "Hot-Carrier Degradation Issues in Advanced CMOS Nodes," in Proc. European Symposium on Reliability of Electron Devices Failure Physics and Analysis (ESREF), tutorial, 2010.

- [8] S. Rauch and G. L. Rosa, "CMOS Hot Carrier: From Physics to End Of Life Projections, and Qualification," in Proc. International Reliability Physics Symposium (IRPS), tutorial, 2010.

- [9] S. Tyaginov, I. Starkov, H. Enichlmair, J. Park, C. Jungemann, and T. Grasser, "Physics-Based Hot-Carrier Degradation Models (invited)," ECS Transactions, vol. 35, no. 4, pp. 321–352, 2011.

- [10] S. Tyaginov and T. Grasser, "Modeling of Hot-Carrier Degradation: Physics and Controversial Issues," in *Proc. International Integrated Reliability Work-shop (IIRW)*, pp. 206–215, 2012.

- [11] C. Hu, S. Tam, F. Hsu, P.-K. Ko, T.-Y. Chan, and K. Terrill, "Hot-electron-induced MOSFET Degradation Model, Monitor and Improvement," *IEEE Trans. Electron Dev.*, vol. 48, no. 4, pp. 375–385, 1985.

- [12] D. DiMaria and J. Stasiak, "Trap Creation in Silicon Dioxide Produced by Hot Electrons," Journ. Appl. Phys., vol. 65, no. 6, pp. 2342–2356, 1989.

- [13] D. DiMaria and J. Stathis, "Anode Hole Injection, Defect Generation, and Breakdown in Ultrathin Silicon Dioxide Films," *Journ. Appl. Phys.*, vol. 89, no. 9, pp. 5015–5024, 2001.

- [14] S. Rauch and G. L. Rosa, "The Energy Driven Paradigm of NMOSFET Hot Carrier Effects," in *Proc. International Reliability Physics Symposium (IRPS)*, 2005.

- [15] S. Rauch and G. L. R. and, "The Energy-Driven Paradigm of NMOSFET Hot-Carrier Effects," *IEEE Trans. Dev. Material. Reliab.*, vol. 5, no. 4, pp. 701–705, 2005.

- [16] E. Takeda and N. Suzuki, "An Empirical Model for Device Degradation due to Hot-Carrier Injection," *IEEE Electron Dev. Lett.*, vol. 4, no. 5, pp. 111–113, 1983.

- [17] B. Doyle, M. Bourcerie, C. Bergonzoni, R. Benecchi, A. Bravis, K. Mistry, and A. Boudou, "The Generation and Characterization of Electron and Hole Traps Created by Hole Injection During Low Gate Voltage Hot-Carrier Stressing of n-MOS Transistors," *IEEE Trans. Electron Dev.*, vol. 37, no. 8, pp. 1869–1876, 1990.

- [18] K. Mistry and B. Doyle, "A Model for AC Hot-Carrier Degradation in n-channel MOSFETs," *IEEE Electron Dev. Lett.*, vol. 12, no. 9, pp. 492–494, 1991.

- [19] J.-S. Goo, Y.-G. Kim, H. Lee, H.-Y. Kwon, and H. Shin, "An Analytical Model for Hot-carrier-induced Degradation of Deep-submicron n-channel LDD MOSFETs," *Solid-State Electron.*, vol. 38, no. 6, pp. 1191–1196, 1995.

- [20] R. Dreesen, K. Croes, J. Manca, W. D. Ceunick, L. D. Schepper, A. Pergoot, and G. Groeseneken, "A New Degradation Model and Lifetime Extrapolation Technique for Lightly Doped Drain nMOSFETs under Hot-Carrier Degradation," *Microel. Reliab.*, vol. 41, pp. 437–443, 2001.

- [21] P. Moens, G. van den Bosch, and G. Groeseneken, "Competing Hot Carrier Degradation Mechanisms in Lateral n-type DMOS Transistors," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 214–221, 2003.

- [22] P. Moens, J. Mertens, F. Bauwens, P. Joris, W. D. Ceuninck, and M. Tack, "A Comprehensive Model for Hot Carrier Degradation in LDMOS Transistors," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 492–497, 2007.

- [23] C. Guerin, V. Huard, and A. Bravaix, "The Energy-Driven Hot Carrier Degradation Modes," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 692–693, 2007.

- [24] A. Bravaix, V. Huard, D. Goguenheim, and E. Vincent, "Hot-carrier to cold-carrier device lifetime modeling with temperature for low power 40nm si-bulk nmos and pmos fets," in *Proc. International Electron Devices Meeting (IEDM)*, pp. 622–625, 2011.

- [25] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmair, M. Karner, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Hot-Carrier Degradation Modeling Using Full-Band Monte-Carlo Simulations," in Proc. International Symposium on the Physical & Failure Analysis of Integrated Circuits (IPFA), 2010.

- [26] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmail, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Interface Traps Density-of-states as a Vital Component for Hot-carrier Degradation Modeling," *Microelectronics Reliability*, vol. 50, pp. 1267–1272, 2010.

- [27] S. Tyaginov, I. Starkov, O. Triebl, H. Enichlmair, C. Jungemann, J. Park, H. Ceric, and T. Grasser, "Secondary Generated Holes as a Crucial Component for Modeling of HC Degradation in High-voltage n-MOSFET," in Proc. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 123–126, 2011.

- [28] S. Rauch, F. Guarin, and G. La Rosa, "Impact of E-E Scattering to the Hot Carrier Degradation of Deep Submicron NMOSFETs," *IEEE Electron Dev. Lett.*, vol. 19, no. 12, pp. 463–465, 1998.

- [29] S. Rauch, G. La Rosa, and F. Guarin, "Role of E-E Scattering in the Enhancement of Channel Hot Carrier Degradation of Deep-Submicron NMOSFETs at high  $V_{\rm gs}$  Conditions," *IEEE Trans. Dev. Material. Reliab.*, vol. 1, no. 2, pp. 113–119, 2001.

- [30] Y. Randriamihaja, V. Huard, X. Federspiel, A. Zaka, P. Palestri, D. Rideau, and A. Bravaix, "Microscopic Scale Characterization and Modeling of Transistor Degradation Under HC Stress," *Microel. Reliab.*, vol. 52, no. 11, pp. 2513–2520, 2012.

- [31] Y. Randriamihaja, X. Federspiel, V. Huard, A. Bravaix, and P. Palestri, "New Hot Carrier Degradation Modeling Reconsidering the Role of EES in Ultra Short n-channel MOSFETs," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 1–5, 2013.

- [32] B. Tuttle and C. V. de Walle, "Structure, Energetics, and Vibrational Properties of Si-H Bond Dissociation in Silicon," Phys. Rev. B, vol. 59, no. 20, pp. 12884–12889, 1999.

- [33] K. Hess, I. C. Kizilyalli, and J. W. Lyding, "Giant Isotope Effect in Hot Electron Degradation of Metal Oxide Silicon Devices," *IEEE Trans Electron Dev.*, vol. 45, no. 2, pp. 406–416, 1998.

- [34] K. Hess, L. Register, B. Tuttle, J. Lyding, and I. Kizilyalli, "Impact of Nanostructure Research on Conventional Solid-State Electronics: the Giant Isotope Effect in Hydrogen Desorption and CMOS Lifetime," *Physica E*, vol. 3, pp. 1–7, 1998.

- [35] T. Mizuno, A. Toriumi, M. Iwase, M. Takanashi, H. Niiyama, M. Fukmoto, and M. Yoshimi, "Hot-carrier Effects in 0.1μm Gate Length CMOS Devices," in Proc. International Electron Devices Meeting (IEDM), pp. 695–698, 1992.

- [36] K. Stokbro, C. Thirstrup, M. Sakurai, U. Quaade, B. Y.-K. Hu, F. Perez-Murano, and F. Grey, "STM-Induced Hydrogen Desorption via a Hole Resonance," Phys. Rev. Lett., vol. 80, pp. 2618–2621, 1998.

- [37] M. Budde, G. Lüpke, E. Chen, X. Zhang, N. H. Tolk, L. C. Feldman, E. Tarhan, A. K. Ramdas, and M. Stavola, "Lifetimes of Hydrogen and Deuterium Related Vibrational Modes in Silicon," *Phys. Rev. Lett.*, vol. 87, no. 4, pp. 1455–1461, 2001.

- [38] R. Walkup, D. Newns, and P. Avouris, "Role of Mutliple Inelastic Transistions in Atom Transfer with the Scanning Tunneling Microscope," *Phys. Rev. B*, vol. 48, no. 3, pp. 1858–1861, 1993.

- [39] J. Lyding, K. Hess, and I. Kizilyalli, "Reduction of Hot Electron Degradation in Metal Oxide Semiconductor Transistors by Deuterium Processing," Appl. Phys. Lett., vol. 68, no. 18, pp. 2526–2528, 1996.

- [40] K. Hess, B. Tuttle, F. Register, and D. Ferry, "Magnitude of the Threshold Energy for Hot Electron Damage in Metal-Oxide-Semiconductor Field Effect Transistors by Hydrogen Desorption," Appl. Phys. Lett., vol. 75, no. 20, pp. 3147–3149, 1999.

- [41] M. Song, K. MacWilliams, and C. Woo, "Comparison of NMOS and PMOS Hot Carrier Effects from 300 to 77 K," *IEEE Trans Electron Dev.*, vol. 44, no. 2, pp. 268–276, 1997.

- [42] J. Wang-Ratkovic, R. Lacoe, K. Williams, M. Song, S. Brown, and G. Yabiku, "New Understanding of LDD CMOS Hot-Carrier Degradation and Device Lifetime at Cryogenic Temperatures," in *Proc. International Reliability Physics* Symposium (IRPS), pp. 312–314, 2003.

- [43] I. Starkov, S. Tyaginov, H. Enichlmair, J. Park, H. Ceric, and T. Grasser, "Analysis of Worst-Case Hot-Carrier Degradation Conditions in the Case of n- and p-channel High-Voltage MOSFETs," in *Proc. International Conference* on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 127– 130, 2011.

- [44] W. Qin, W. Chim, D. H. Chan, and C. Lou, "Modelling the Degradation in the Subthreshold Characteristics of Submicrometre LDD PMOSFETs under Hot-Carrier Stressing," Semicond. Sci. Technol., vol. 13, no. 5, pp. 453–459, 1998.

- [45] S. Manzini and A. Gallerano, "Avalanche Injection of Hot Holes in the Gate Oxide of LDMOS," *Solid-State Electron.*, vol. 44, no. 1, pp. 1325–1330, 2000.

- [46] E. Li, E. Rosenbaum, J. Tao, G.-F. Yeap, M. Lin, and P. Fang, "Hot-carrier Effects in nMOSFETs in 0.1 μm CMOS Technology," in Proc. International Reliability Physics Symposium (IRPS), pp. 253–258, 1999.

- [47] C. Lin, S. Biesemans, L. Han, K. Houlihan, T. Schiml, K. Schruefer, C. Wann, and R. Markhopf, "Hot Carrier Reliability for 0.13 μm CMOS Technology with Dual Gate Oxide Thickness," in Proc. International Electron Devices Meeting (IEDM), pp. 135–138, 2000.

- [48] R. Woltjer, A. Hamada, and E. Takeda, "PMOSFET Hot Carrier Damage: Oxide Charge and Interface States," Semicond Sci. Technol., vol. 7, pp. pp. B581–B584, 1992.

- [49] A. Bravaix, D. Goguenheim, N. Revil, and E. Vincent, "Hole Injection Enhanced Hot-Carrier Degradation in PMOSFETs Used for Systems on Chip Applications with 6.5-2 nm Thick Gate Oxides," *Microel. Reliab.*, vol. 44, no. 1, pp. 65–77, 2004.

- [50] J. Bude and K. Hess, "Thresholds of Impact Ionization in Semiconductors," Journal of Applied Physics, vol. 72, no. 8, pp. 3554–3561, 1992.

- [51] F. Venturi, E. Sangiorgi, and B. Ricco, "The Impact of Voltage Scaling on Electron Heating and Device Performance of Submicrometer MOSFET's," IEEE Trans. Electron Dev., vol. 38, no. 8, pp. 1895–1904, 1991.

- [52] J. Chung, M. Jeng, J. Moon, P. Ko, and C. Hu, "Low-voltage hot-electron currents and degradation in deep-submicrometer mosfets," *IEEE Trans. Electron Dev.*, vol. 37, pp. 1651–1657, 1990.

- [53] P. Childs and C. Leung, "New Mechanism of Hot Carrier Generation in Very Short Channel MOSFETs," *Electronics Letters*, vol. 31, no. 2, pp. 139–141, 1995.

- [54] P. Childs and C. Leung, "A Onedimensional Solution of the Boltzmann Transport Equation Including Eelectron–Electron Interactions," *Journal of Applied Physics*, vol. 79, no. 1, pp. 222–227, 1996.

- [55] F.-C. Hsu and K.-Y. Chu, "Temperature Dependence of Hot-Electron Induced Degradation in MOSFETs," *IEEE Electron Dev. Lett.*, vol. 5, no. 5, pp. 148– 150, 1984.

- [56] P. Heremans, G. V. den Bosch, R. Bellens, G. Groseneken, and H. Maes, "Temperature Dependence of the Channel Hot-Carrier Degradation of n-channel MOSFETs," *IEEE Trans. Electron Dev.*, vol. 37, no. 4, pp. 980–992, 1990.

- [57] A. Bravaix, D. Goguenheim, N. Revil, E. Vincent, M. Varrot, and P. Mortini, "Analysis of High Temperatures Effects on Performance and Hot-Carrier Degradation in DC/AC Stressed 0.35  $\mu$ m n-MOSFETs," *Microel. Reliab.*, vol. 39, no. 1, pp. 35–44, 1999.

- [58] H. Enichlmair, S. Carniello, J. Park, and R. Minixhofer, "Analysis of Hot Carrier Effects in a 0.35  $\mu$ m High Voltage n-channel LDMOS," *Microel. Reliab.*, vol. 47, no. 9-11, pp. 1439–1443, 2007.

- [59] K. Lee, O. Yoo, R. Choi, B. Lee, J. Lee, H.-D. Lee, and Y.-H. Jeong, "PBTI-Associated High-Temperature Hot Carrier Degradation of nMOSFETs with Metal-Gate/High-k Dielectrics," *IEEE Electron Dev. Lett.*, vol. 29, no. 4, pp. 389–391, 2008.

- [60] M. Jo, S. Kim, C. Cho, M. Chang, and H. Hwang, "Gate Voltage Dependence on Hot Carrier Degradation at an Elevated Temperature in a Device with Ultrathin Silicon Oxynitride," Appl. Phys. Lett., vol. 94, no. 5, pp. 053505-1-053505-3, 2009.

- [61] E. Amat, T. Kauerauf, R. Degraeve, R. Rodriguez, M. Nafria, X. Aymerich, and G. Groeseneken, "Channel Hot-Carrier Degradation in pMOS and nMOS

- Short Channel Transistors with High-k Dielectric Stack," *Microel. Engineering*, vol. 87, no. 1, pp. 47–50, 2010.

- [62] Y. Leblebici and S.-M. Kang, "Modeling of nMOS Transistors for Simulation of Hot-Carrier Induced Device and Circuit Degradation," *IEEE Transaction* on Computer-Aided Design, vol. 11, no. 2, pp. 235–246, 1992.

- [63] S. Cristoloveanu, H. Haddara, and N. Revil, "Defect Localization Induced by Hot Carrier Injection in Short-Channel MOSFETs: Concept, Modeling and Characterization," *Microel. Reliab.*, vol. 33, no. 9, pp. 1365–1385, 1993.

- [64] A. Acovic, G. L. Rosa, and Y. Sun, "A Review of Hot Carrier Degradation Mechanism in MOSFETs," *Microel. Reliab.*, vol. 36, no. 7/8, pp. 845–869, 1996.

- [65] I. Starkov, H. Enichlmair, S. Tyaginov, and T. Grasser, "Charge-Pumping Extraction Techniques for Hot-Carrier Induced Interface and Oxide Trap Spatial Distributions in MOSFETs," in *Proc. International Symposium on the Physical & Failure Analysis of Integrated Circuits (IPFA)*, pp. 1–6, 2012.

- [66] I. Starkov, H. Enichlmair, S. Tyaginov, and T. Grasser, "Analysis of the Threshold Voltage Turn-Around Effect in High-Voltage n-MOSFETs due to Hot-Carrier Stress," in *Proc. International Reliability Physics Symposium* (IRPS), p. 6 pages, 2012.

- [67] K. Rupp, T. Grasser, and A. Jungel, "On the Feasibility of Spherical Harmonics Expansions of the Boltzmann Transport Equation for Three-Dimensional Device Geometries," in *Proc. International Electron Devices Meeting (IEDM)*, pp. 789–792, 2011.

- [68] K. Rupp, C. Jungemann, M. Bina, A. Jüngel, and T. Grasser, "Bipolar Spherical Harmonics Expansions of the Boltzmann Transport Equation," in Proc. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 19–22, 2012.

- [69] K. Rupp, P. Lagger, T. Grasser, and A. Jüngel, "Inclusion of Carrier-Carrier-Scattering into Arbitrary-Order Spherical Harmonics Expansions of the Boltzmann Transport Equation," in *Proc. International Workshop on Computational Electronics (IWCE)*, pp. 1–4, 2012.

- [70] S. Tyaginov, M. Bina, J. Franco, D. Osintsev, O. Triebl, B. Kaczer, and T. Grasser, "Physical Modeling of Hot-Carrier Degradation for Short- and Long-Channel MOSFETs," in *Proc. International Reliability Physics Sympo*sium (IRPS), pp. XT.16–1–16–8, 2014.

- [71] M. Bina, S. Tyaginov, J. Franco, Y. Wimmer, D. Osinstev, B. Kaczer, T. Grasser, et al., "Predictive Hot-Carrier Modeling of n-channel MOSFETs," IEEE Transactions on Electron Devices, vol. in press, 2014.

- [72] J. McPherson, "Quantum Mechanical Treatment of Si-O Bond Breakage in Silica Under Time Dependent Dielectric Breakdown Testing," in *Proc. Inter*national Reliability Physics Symposium (IRPS), pp. 209–216, 2007.

- [73] C. Guerin, V. Huard, and A. Bravaix, "General Framework about Defect Creation at the Si/SiO<sub>2</sub> Interface," *Journ. Appl. Phys.*, vol. 105, pp. 114513–1–114513–12, 2009.

- [74] A. Stesmans, "Revision of H<sub>2</sub> Passivation of P<sub>2</sub> Interface Defects in Standard (111)Si/SiO<sub>2</sub>," Applied Physics Letters, vol. 68, no. 19, pp. 2723–2725, 1996.

- [75] A. Stesmans, "Passivation of  $P_{b0}$  and  $P_{b1}$  Interface Defects in Thermal (100) Si/SiO<sub>2</sub> with Molecular Hydrogen," *Appl. Phys. Lett.*, vol. 68, no. 15, pp. 2076–2078, 1996.

- [76] G. Pobegen, S. Tyaginov, M. Nelhiebel, and T. Grasser, "Observation of Normally Distributed Activation Energies for the Recovery from Hot Carrier Damage," *IEEE Electron Dev. Lett.*, vol. 34, no. 8, pp. 939–941, 2013.

- [77] Synopsis, Sentaurus Process, Advanced Simulator for Process Technologies.

- [78] Y. Randriamihaja, A. Zaka, V. Huard, M. Rafik, D. Rideau, D. Roy, A. Bravaix, and P. Palestri, "Hot Carrier Degradation: From Defect Creation Modeling to Their Impact on NMOS Parameters," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 1–4, 2012.